[ad_1]

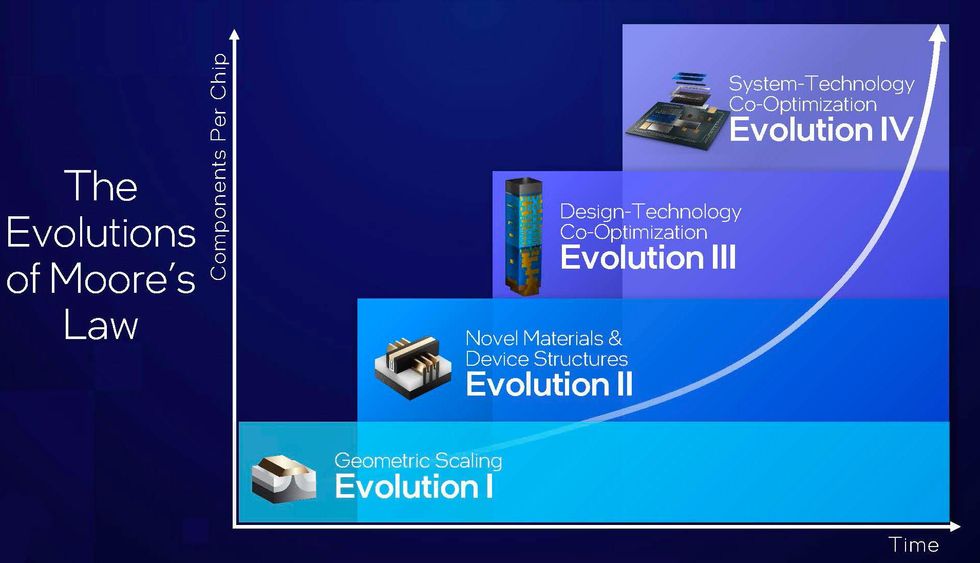

The subsequent wave of Moore’s Law will depend on a growing idea known as system expertise co-optimization, Ann B. Kelleher, normal supervisor of expertise growth at Intel informed IEEE Spectrum in an interview forward of her plenary speak on the 2022 IEEE Electron Device Meeting.

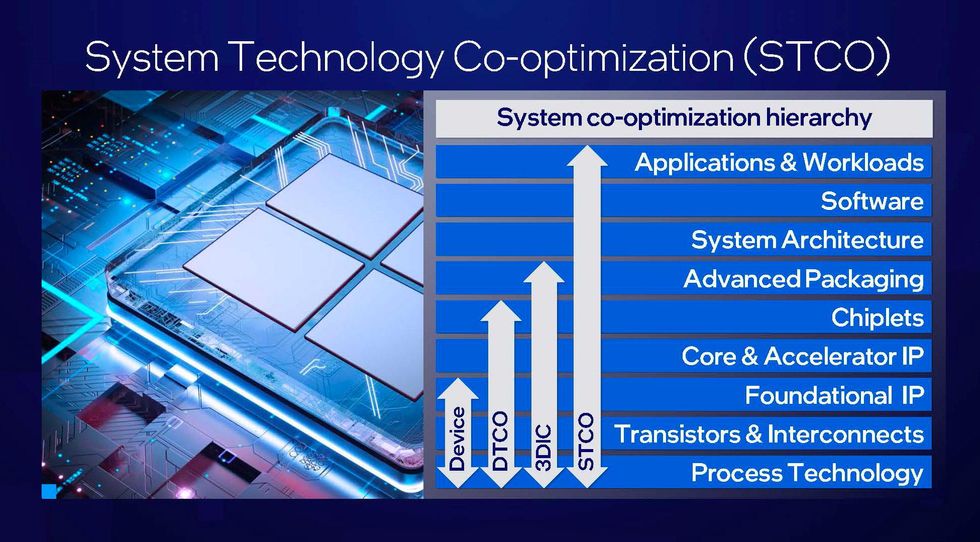

“Moore’s Law is about increasing the integration of functions,” says Kelleher. “As we look forward into the next 10 to 20 years, there’s a pipeline full of innovation” that can proceed the cadence of improved merchandise each two years. That path consists of the standard continued enhancements in semiconductor processes and design, however system expertise co-optimization (STCO) will make the largest distinction.

Kelleher calls it an “outside-in” method of growth. It begins with the workload a product must help and its software program, then works all the way down to system structure, then what kind of silicon have to be inside a bundle, and eventually all the way down to the semiconductor manufacturing course of. “With system technology co-optimization, it means all the pieces are optimized together so that you’re getting your best answer for the end product,” she says.

STCO is an possibility now largely as a result of superior packaging, resembling 3D integration, is permitting the high-bandwidth connection of chiplets—small, purposeful chips—inside a single bundle. This signifies that what would as soon as be capabilities on a single chip could be disaggregated onto devoted chiplets, which may every then be made utilizing essentially the most optimum semiconductor course of expertise. For instance, Kelleher factors out in her plenary that high-performance computing calls for a considerable amount of cache reminiscence per processor core, however chipmaker’s capacity to shrink SRAM will not be continuing on the identical tempo because the cutting down of logic. So it is smart to construct SRAM caches and compute cores as separate chiplets utilizing totally different course of expertise after which sew them collectively utilizing 3D integration.

A key instance of STCO in motion, says Kelleher, is the Ponte Vecchio processor on the coronary heart of the Aurora supercomputer. It’s composed of 47 energetic chiplets (in addition to 8 blanks for thermal conduction). These are stitched collectively utilizing each superior horizontal connections (2.5 packaging tech) and 3D stacking. “It brings together silicon from different fabs and enables them to come together so that the system is able to perform against the workload that it’s designed for,” she says.

At IEDM, Intel engineers will report that they’ve elevated the density of their 3D hybrid bonding expertise ten-fold versus what they reported in 2021. Increased connection density means extra chip capabilities could be disaggregated onto separate chiplets, in flip offering extra potential to make use of STCO to enhance outcomes. Hybrid bond pitches, which means the space between the interconnects, are simply 3 micrometers with this new expertise. With that, much more cache could be separated from the processor cores. Reducing the bond pitch to between 2 micrometers and 100 nanometers may imply having the ability to begin pulling aside logic capabilities that right this moment have to be on the identical piece of silicon, in keeping with Kelleher.

The drive to optimize techniques by disaggregating capabilities is having penalties for future semiconductor manufacturing processes. Future semiconductor course of expertise has to take care of the thermal stresses of a 3D-packaged atmosphere. But interconnect expertise will most likely see the largest change. Kelleher says Intel is on monitor to introduce a expertise it calls PowerVia (bottom energy supply, extra typically) in 2024. PowerVia strikes a chip’s energy supply community beneath the silicon, decreasing the scale of logic cells and chopping energy consumption. But it additionally “gives us different opportunities in terms of what we can and how we can interconnect in the package,” says Kelleher.

Kelleher stresses that STCO continues to be in its infancy. Electronic design automation (EDA) instruments have already tackled STCO’s predecessor, design expertise co-optimization (DTCO), which focuses on logic-cell degree and functional-block degree optimizations. “But some of the EDA tool vendors are already working on this,” she says. “Going forward, the focus is going to be on the methods and tools that help enable STCO.”

As STCO develops, gadget engineers could should develop with it. “Generally, engineers will need to continue to have their device knowledge but also begin to understand the use cases of their technology and their devices,” says Kelleher. “More interdisciplinary skills will be required as we head into more of an STCO world.”

Intel’s Roadmap

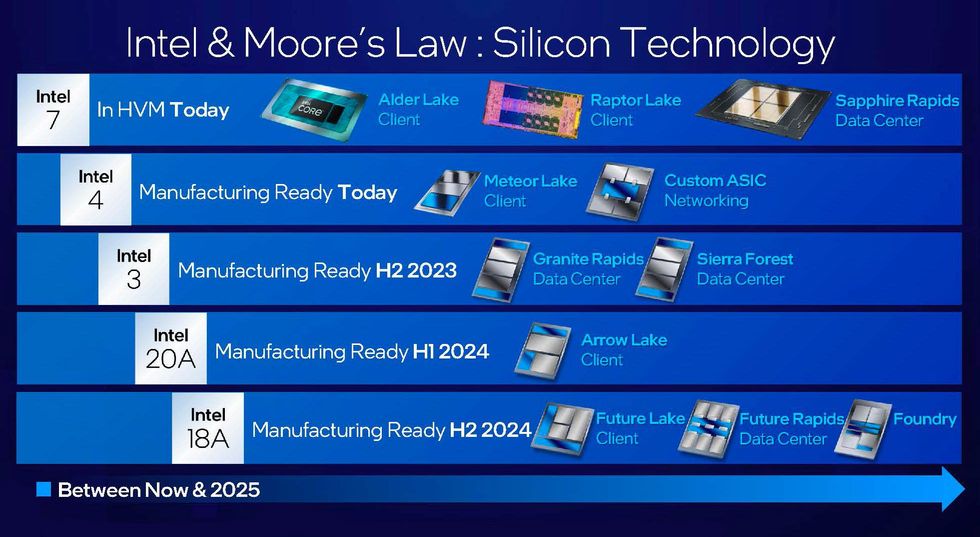

Kelleher additionally up to date Intel’s roadmap, tying it in with the development of Moore’s Law and the evolution of the gadget for the reason that invention of the primary transistor. The backside line is that issues are on monitor from when Intel introduced its new manufacturing roadmap lower than two years in the past, in keeping with Kelleher. But she did fill in some particulars of which processors would debut with the brand new tech.

Intel 20A, due for manufacturing introduction within the first half of 2024, stays the large technological leap. It concurrently introduces a brand new transistor structure—RibbonFET (extra typically known as gate-all-around or nanosheet transistors)—and PowerVia bottom energy supply. Asked in regards to the threat concerned, Kelleher defined the technique.

“They do not have to be done at once, but we see significant benefits from moving to PowerVia to enable the [RibbonFET] technology,” she says. The growth is going on in parallel to cut back the chance of delays, she explains. Intel is working a check course of utilizing FinFETs, the transistor structure in use right this moment, with PowerVia. “That has been working very successfully and it has enabled us to accelerate our development work,” she says.

The Transistor of the Future

Kelleher’s speak comes because the IEEE Electron Device Society celebrates the seventy fifth anniversary of the invention of the transistor. At IEEE Spectrum, we requested specialists what the transistor is likely to be like on its a centesimal birthday in 2047. Kelleher’s take took within the long-lifetimes of transistor expertise, noting that the planar transistor design lasted from 1960 to about 2010, and that its successor the FinFET continues to be going robust. “Now we’re going to the RibbonFET which is going to last for probably another 20-plus years… so I expect we’re going to be somewhere with stacked RibbonFETs,” she steered. [Intel engineers describe that technology in the December 2022 issue of IEEE Spectrum.] However, by that point, the ribbons could also be fabricated from 2D semiconductors as a substitute of silicon.

From Your Site Articles

Related Articles Around the Web

[ad_2]